Port Mapping

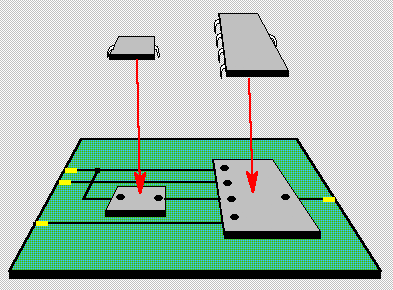

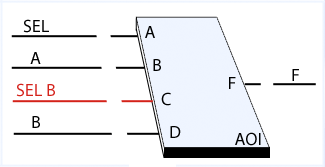

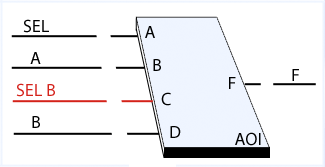

The concept of port mapping is little more than soldering the chip socket pins into the holes of the PCB. Thus in the case of our inverter, the F output pin of the INV chip is plugged into the F pin of the INV socket. The F pin of the INV socket is soldered to a PCB trace called SELB.

Similarly, instantiation of the AOI gate can be thought of as soldering the AOI socket into the MUX2I PCB. In this case, as an example, the SELB trace is soldered to the C pin of the AOI socket. By default, the AOI socket is assumed to be carrying an AOI chip.

architecture STRUCTURE of MUX2I is

...

component AOI

port (A, B, C, D: in STD_LOGIC; -- 3rd item in list is C

F : out STD_LOGIC);

end component;

signal SELB: STD_LOGIC;

begin

...

G2: AOI port map (SEL, A, SELB, B, F); -- 3rd item in list is SELB

end;

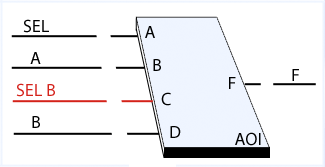

Default binding

Our current view of component instantiation assumes default binding. In default binding, the chip socket (component declaration) carries a chip (design entity) of the same name (say, AOI) as we've already seen. Now in the hardware world, there's no such limitation, sockets aren't chip specific. VHDL allows the designer the same freedom. The chip socket and the chip do not have to have the same name, but to implement this facility requires a configuration to bind the appropriate design entity to the component instantiation. We'll look at configurations shortly.

Prev Next

Your e-mail comments are welcome - send email

Copyright 1995-2016 Doulos